| Surname       | Centre<br>Number | Candidate<br>Number |

|---------------|------------------|---------------------|

| First name(s) |                  | 2                   |

TUESDAY, 24 MAY 2022 – AFTERNOON

### ELECTRONICS – AS component 1 Principles of Electronics

2 hours 30 minutes

| For Examiner's use only |                 |                 |  |  |

|-------------------------|-----------------|-----------------|--|--|

| Question                | Maximum<br>Mark | Mark<br>Awarded |  |  |

| 1.                      | 11              |                 |  |  |

| 2.                      | 13              |                 |  |  |

| 3.                      | 15              |                 |  |  |

| 4.                      | 10              |                 |  |  |

| 5.                      | 8               |                 |  |  |

| 6.                      | 7               |                 |  |  |

| 7.                      | 6               |                 |  |  |

| 8.                      | 8               |                 |  |  |

| 9.                      | 13              |                 |  |  |

| 10.                     | 17              |                 |  |  |

| 11.                     | 12              |                 |  |  |

| Total                   | 120             |                 |  |  |

#### ADDITIONAL MATERIALS

In addition to this examination paper, you will require a calculator and a **Data Booklet**.

#### **INSTRUCTIONS TO CANDIDATES**

Use black ink or black ball-point pen. Do not use gel pen or correction fluid.

You may use a pencil for graphs and diagrams only.

Write your name, centre number and candidate number in the spaces at the top of this page. Answer **all** questions.

Write your answers in the spaces provided in this booklet. If you run out of space, use the additional page(s) at the back of the booklet, taking care to number the question(s) correctly.

#### **INFORMATION FOR CANDIDATES**

The number of marks is given in brackets at the end of each question or part-question. The assessment of the quality of extended response (QER) will take place in questions **3**(b) and **7**.

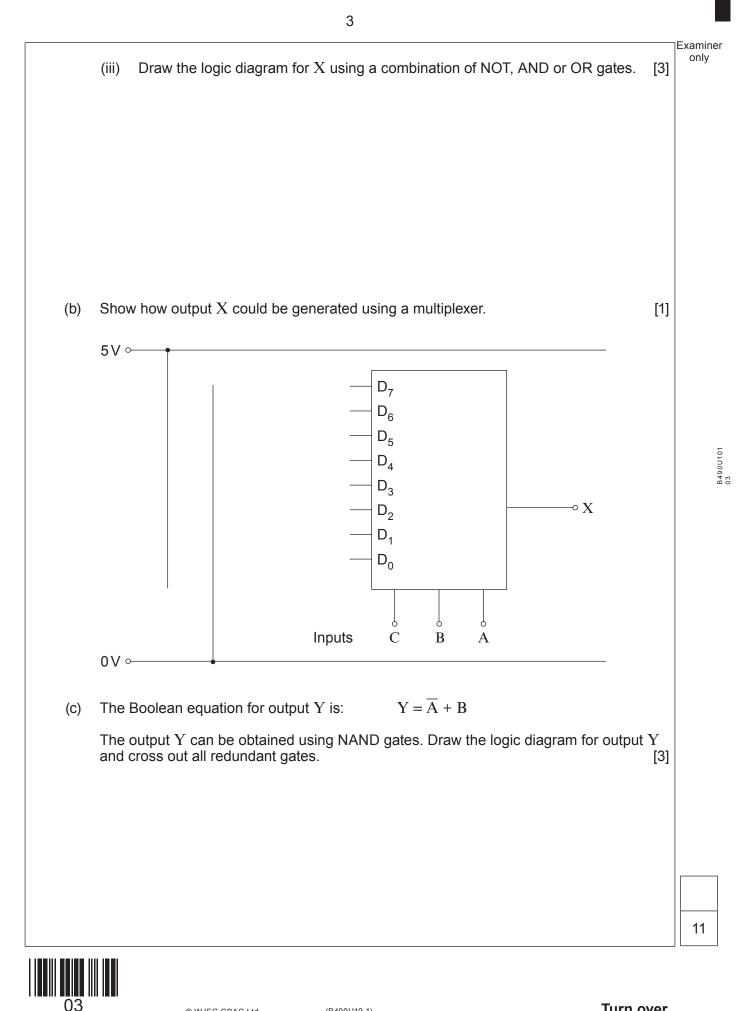

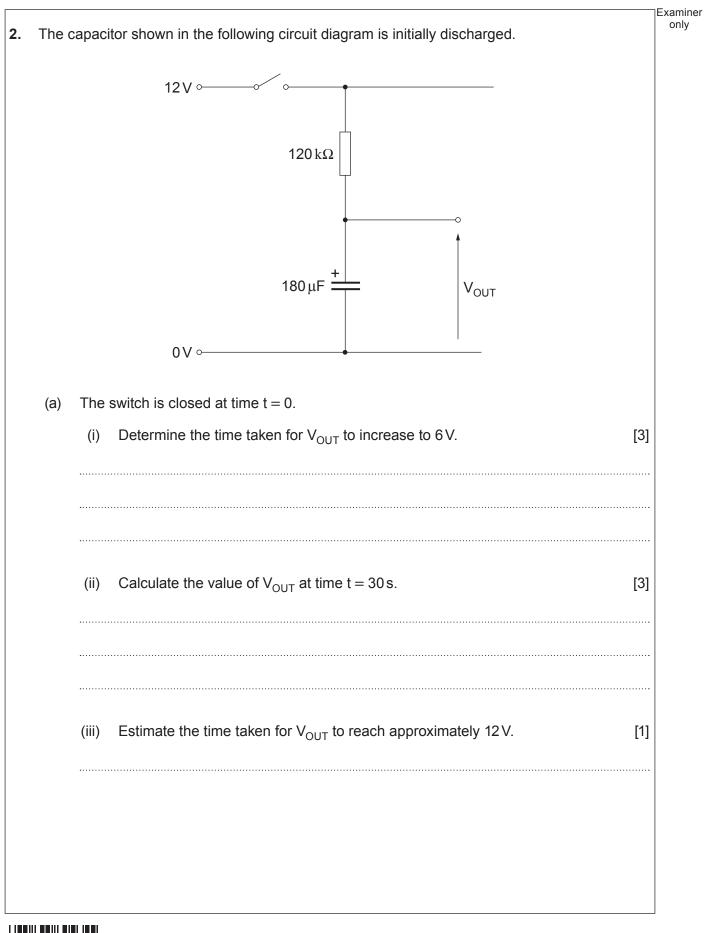

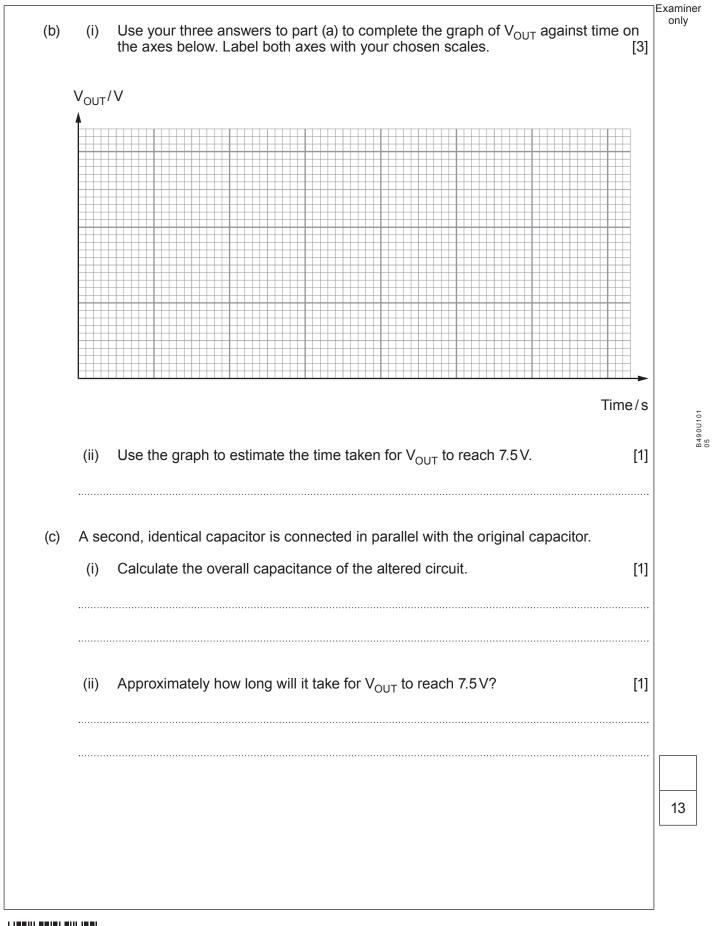

Examiner only Answer all questions. A logic system has two outputs X and Y. 1. The system gives the following truth table for output X. (a) С В Α Х Use the truth table to write down the **unsimplified** Boolean equation for output  $\boldsymbol{X}$ (i) in terms of C, B and A. [1] X = ..... (ii) Complete the Karnaugh map and determine the simplest equation for output X. [3] BA С ..... X = .....

© WJEC CBAC Ltd.

(B490U10-1)

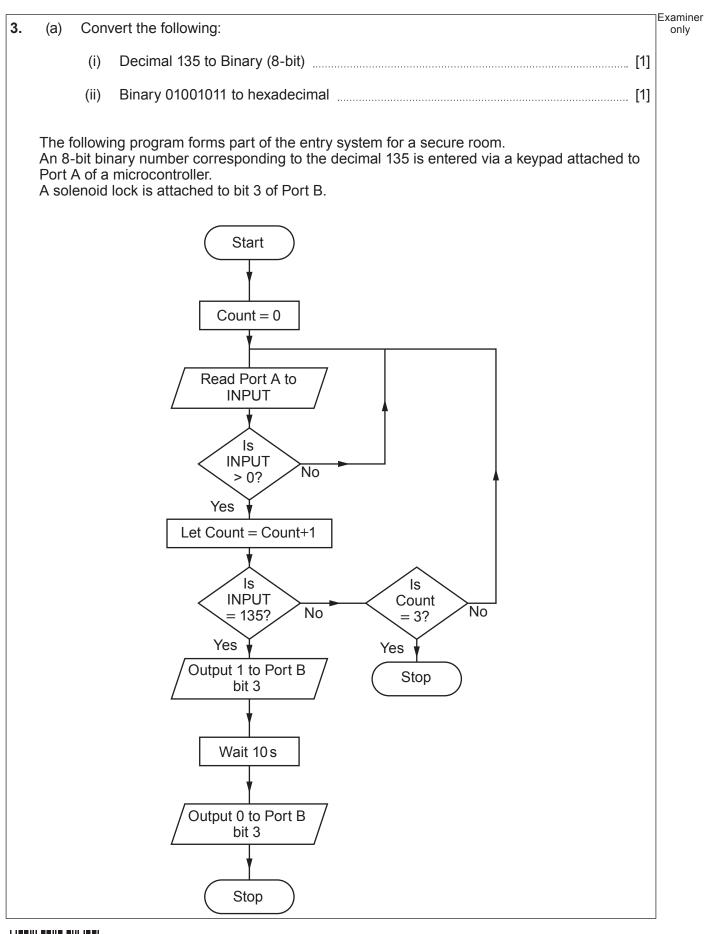

Examiner Analyse the flow chart and explain in detail how the program operates. [6 QER] (b) ..... ..... ..... ..... ..... \_\_\_\_\_ ..... .....

7

only

| (c) The  | e circuit diagram for the solenoid lock is shown below.                                                                                                                          | Exa      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|          | 24 V o<br>Solenoid 24 V, 3 A                                                                                                                                                     |          |

|          | Output from<br>Port B o<br>bit 3                                                                                                                                                 |          |

|          | 0 V o                                                                                                                                                                            |          |

| (i)      | Explain why the diode is needed in this circuit.                                                                                                                                 | [1]      |

| <b>.</b> |                                                                                                                                                                                  |          |

| (ii)<br> |                                                                                                                                                                                  | e<br>[3] |

|          | at its rated current. Calculate the value of the transconductance g <sub>M</sub> .<br>The MOSFET dissipates a power of 1.5W when the solenoid is operating at its rated current. |          |

| ······   | at its rated current. Calculate the value of the transconductance g <sub>M</sub> .<br>The MOSFET dissipates a power of 1.5W when the solenoid is operating at its rated current. | [3]      |

## **BLANK PAGE**

9

## **PLEASE DO NOT WRITE ON THIS PAGE**

© WJEC CBAC Ltd.

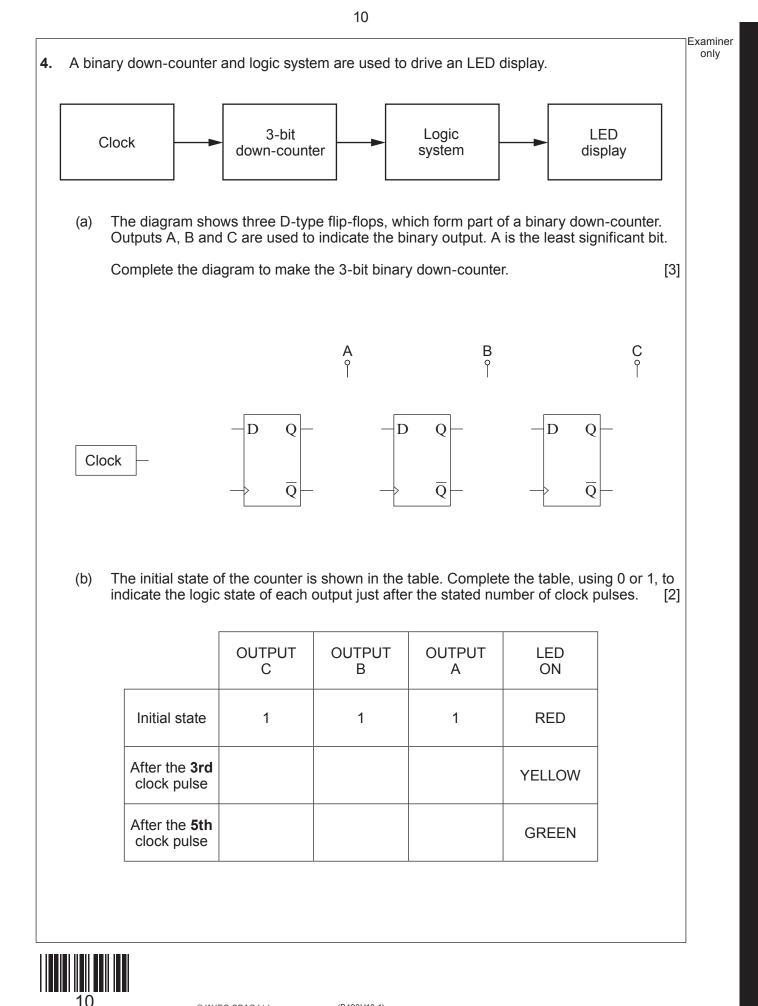

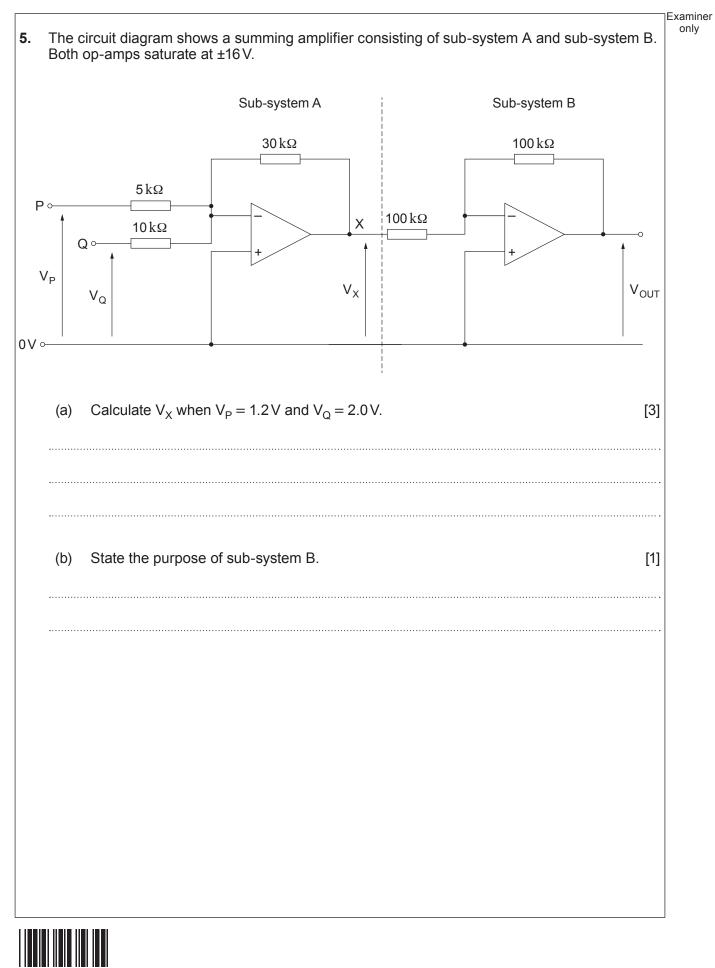

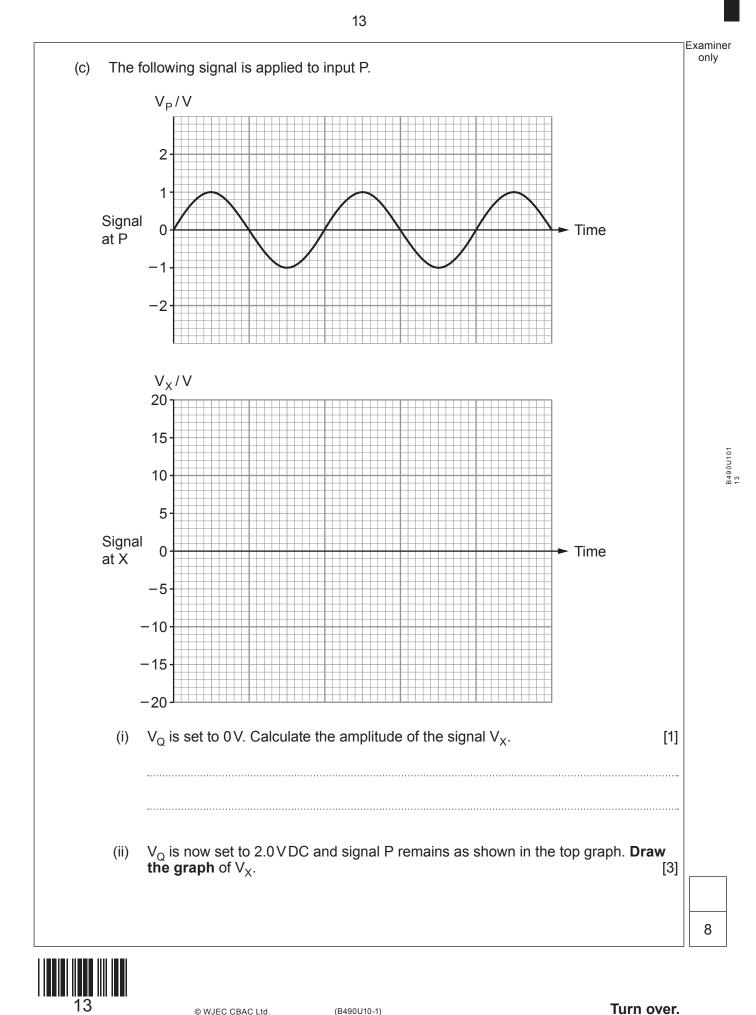

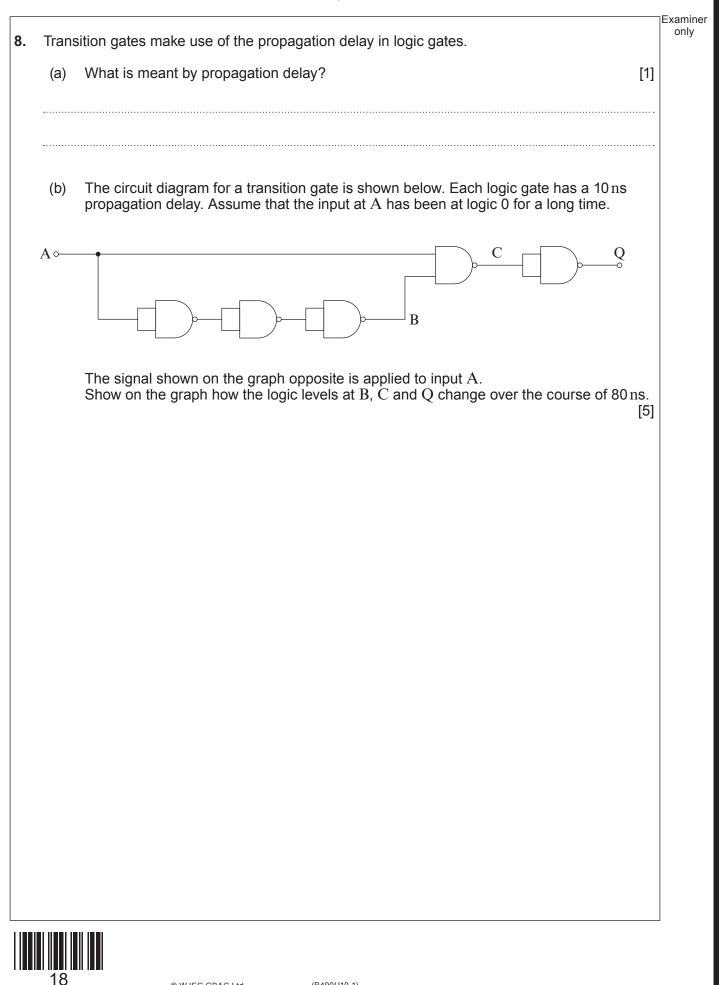

Examiner only The system is used to light LEDs in sequence. On the diagram below, add the necessary logic gates and connections so that the yellow LED lights on the **3rd** (C) (i) pulse only. [2] 3-bit downcounter Clock С В A Yellow LED **120**Ω 0V ~ B490U101 11 The forward voltage drop across the LED is 2.1 V. When the output of a logic gate is 5 V, calculate the current that flows through the LED. (ii) [3] ..... \_\_\_\_\_ 10

11

© WJEC CBAC Ltd.

© WJEC CBAC Ltd.

| 6. | The f    | ollowii           | ng diagram shows a logic system.                                                                                                                                 | Examine<br>only |

|----|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|    |          | A ↔<br>B ↔<br>C ↔ | Logic<br>Gate<br>P<br>T                                                                                                                                          |                 |

|    | (a)      | (i)               | The signal at point S is given by the Boolean equation $S = (\overline{B + A})$ . Identify logic gate P. [1]                                                     |                 |

|    |          | (ii)              | Write down the Boolean equations for T and Q in terms of inputs A, B and C. [2] $T = $ $Q = $                                                                    |                 |

|    | (b)      |                   | engineer produces the following Boolean equation as a solution to<br>of a design problem.<br>$Q = (\overline{\overline{C + A}) + (\overline{\overline{B}.A})}$   |                 |

|    |          | Appl              | Ileague suggests that one of the inputs is not needed.<br>y de Morgan's theorem to this equation and simplify it to identify the input that is<br>needed.<br>[4] |                 |

|    |          |                   |                                                                                                                                                                  |                 |

|    | <u>.</u> | The               | input not needed is                                                                                                                                              |                 |

## **BLANK PAGE**

15

## **PLEASE DO NOT WRITE ON THIS PAGE**

|                             | DN for 3s each cycle.                                                            |                                                    |

|-----------------------------|----------------------------------------------------------------------------------|----------------------------------------------------|

| A design for the sy         | stem is shown below.                                                             |                                                    |

| 5V o                        | •                                                                                |                                                    |

|                             | $R_1$ 4.8 k $\Omega$                                                             |                                                    |

|                             | 7 4<br>6 55                                                                      | 120 Ω                                              |

|                             | $R_2$ 9.6 k $\Omega$ 2 1                                                         |                                                    |

|                             | •                                                                                | 10 nF                                              |

|                             | C 30 μF                                                                          |                                                    |

| 0 V ⊶<br>Evaluate the desig | n shown in the diagram against the syst                                          | em specification <b>and</b> suggest any            |

| Evaluate the desig          | C 30 μF                                                                          | em specification <b>and</b> suggest any<br>[6 QER] |

| Evaluate the desig          | n shown in the diagram against the syst<br>ired to meet the specification fully. | em specification <b>and</b> suggest any<br>[6 QER] |

| Evaluate the desig          | n shown in the diagram against the syst<br>ired to meet the specification fully. | [6 QER]                                            |

| Evaluate the desig          | n shown in the diagram against the syst<br>ired to meet the specification fully. | [6 QER]                                            |

| Evaluate the desig          | n shown in the diagram against the syst<br>ired to meet the specification fully. | [6 QER]                                            |

| Evaluate the desig          | n shown in the diagram against the syst<br>ired to meet the specification fully. | [6 QER]                                            |

|                                           | Examiner |

|-------------------------------------------|----------|

|                                           | only     |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           |          |

|                                           | 6        |

|                                           |          |

|                                           |          |

|                                           |          |

| 17 © WJEC CBAC Ltd. (B490U10-1) Turn over | _        |

Turn over.

(B490U10-1)

|     |           | 22                                                                                     |                        |

|-----|-----------|----------------------------------------------------------------------------------------|------------------------|

| (d) | (i)       | Draw a circuit diagram for an op-amp voltage follower. [2                              | Examiner<br>only<br>2] |

|     | (ii)      | What is the input impedance of this circuit? [1                                        | ]                      |

|     | (iii)<br> | What is the output voltage from this circuit when a 3.2V DC input signal is applied [1 | ?<br> ]                |

|     |           |                                                                                        | 13                     |

|     |           |                                                                                        |                        |

|     |           |                                                                                        |                        |

|     |           |                                                                                        |                        |

| 22  |           | © WJEC CBAC Ltd. (B490U10-1)                                                           |                        |

# **BLANK PAGE**

23

### PLEASE DO NOT WRITE ON THIS PAGE

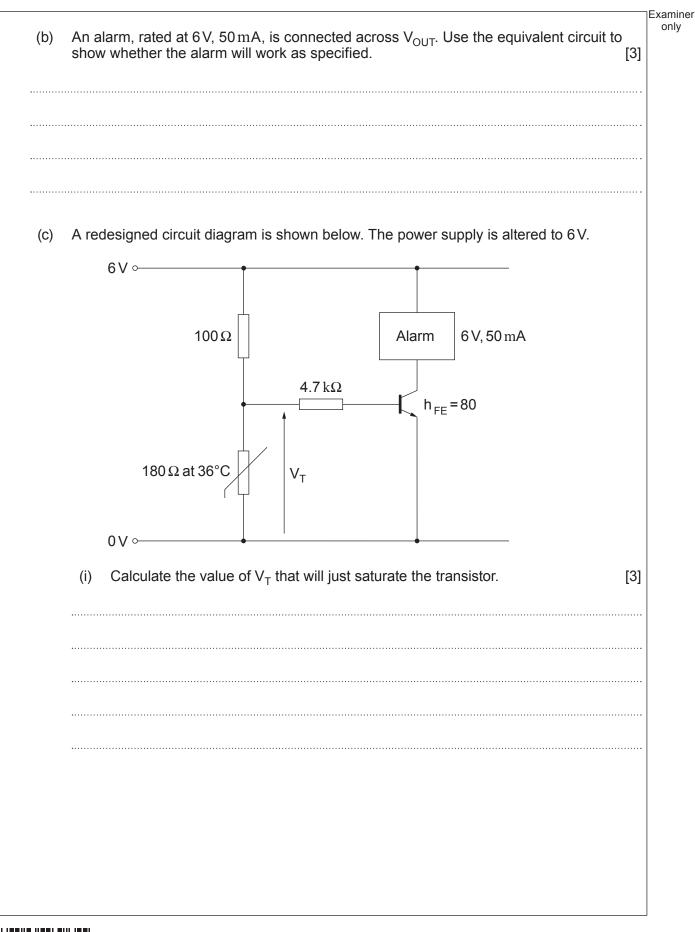

Examiner only **10.** A project brief requires a student to design a temperature sensing system that will sound an alarm if a patient's temperature falls below 36 °C. The temperature sensing sub-system is shown below. The resistance of the thermistor is  $180\Omega$  at 36 °C. 12V ∽ 100 Ω -0  $180\,\Omega$  at  $36^\circ$ V<sub>OUT</sub> 0V ~ Thevenin's theorem is used to produce an equivalent circuit. Calculate the open (a) (i) circuit voltage  $V_{OC}$  and the equivalent resistance  $R_{EQ}$ . [5] (ii) Draw the equivalent circuit. [1]

© WJEC CBAC Ltd.

| (ii) Evaluate whether the alarm will now work as specified. | [5 |

|-------------------------------------------------------------|----|

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

## **BLANK PAGE**

27

### PLEASE DO NOT WRITE ON THIS PAGE

© WJEC CBAC Ltd.

| Question number | Additional page, if required.<br>Write the question number(s) in the left-hand margin. | Examiner<br>only |

|-----------------|----------------------------------------------------------------------------------------|------------------|

|                 |                                                                                        | 1                |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

|                 |                                                                                        |                  |

### PLEASE DO NOT WRITE ON THIS PAGE