Surname

0

Other Names

GCSE

# 4162/01

# ELECTRONICS UNIT E2: Paper replacement test

FRIDAY, 15 JUNE 2018 - AFTERNOON

1 hour

| For Examiner's use only |                 |                 |  |  |  |  |  |

|-------------------------|-----------------|-----------------|--|--|--|--|--|

| Question                | Maximum<br>Mark | Mark<br>Awarded |  |  |  |  |  |

| 1.                      | 5               |                 |  |  |  |  |  |

| 2.                      | 3               |                 |  |  |  |  |  |

| 3.                      | 3               |                 |  |  |  |  |  |

| 4.                      | 4               |                 |  |  |  |  |  |

| 5.                      | 3               |                 |  |  |  |  |  |

| 6.                      | 2               |                 |  |  |  |  |  |

| 7.                      | 4               |                 |  |  |  |  |  |

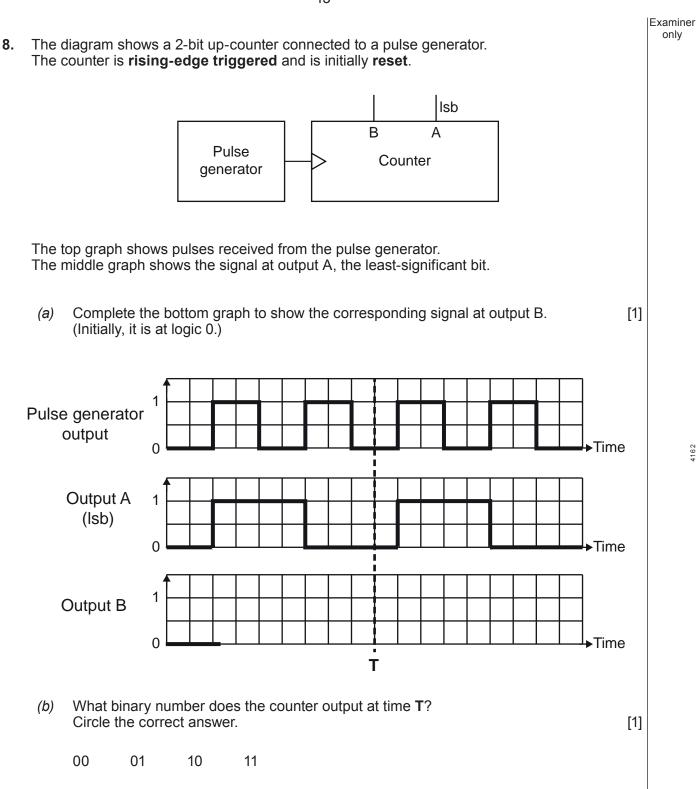

| 8.                      | 2               |                 |  |  |  |  |  |

| 9.                      | 4               |                 |  |  |  |  |  |

| 10.                     | 2               |                 |  |  |  |  |  |

| 11.                     | 5               |                 |  |  |  |  |  |

| 12.                     | 3               |                 |  |  |  |  |  |

| 13.                     | 3               |                 |  |  |  |  |  |

| 14.                     | 5               |                 |  |  |  |  |  |

| 15.                     | 4               |                 |  |  |  |  |  |

| 16.                     | 5               |                 |  |  |  |  |  |

| 17.                     | 3               |                 |  |  |  |  |  |

| Total                   | 60              |                 |  |  |  |  |  |

## ADDITIONAL MATERIALS

A calculator and a ruler.

## INSTRUCTIONS TO CANDIDATES

Use black ink or black ball-point pen.

Write your name, centre number and candidate number in the spaces at the top of this page.

Answer **all** questions in the spaces provided in this booklet.

## INFORMATION FOR CANDIDATES

The number of marks is given in brackets at the end of each question or part-question.

#### **INFORMATION SHEET FOR UNIT E2**

This information may be of use in answering the questions.

1. Resistor Colour Codes

| BLACK  | 0 | GREEN  | 5 |

|--------|---|--------|---|

| BROWN  | 1 | BLUE   | 6 |

| RED    | 2 | VIOLET | 7 |

| ORANGE | 3 | GREY   | 8 |

| YELLOW | 4 | WHITE  | 9 |

The fourth band colour gives the tolerance as follows:

| GOLD   | ± | 5%  |

|--------|---|-----|

| SILVER | ± | 10% |

#### 2. Preferred Values for Resistors – E24 series

10, 11, 12, 13, 15, 16, 18, 20, 22, 24, 27, 30, 33, 36, 39, 43, 47, 51, 56, 62, 68, 75, 82, 91.

- 3. Resistance =  $\frac{\text{voltage}}{\text{current}}$ ; R =  $\frac{\text{V}}{\text{I}}$ .

- 4. Effective resistance, R, of two resistors  $R_1$  and  $R_2$  in series is given by  $R = R_1 + R_2$ .

- 5. Effective resistance, R, of two resistors R<sub>1</sub> and R<sub>2</sub> in parallel is given by  $R = \frac{R_1R_2}{R_1 + R_2}$ .

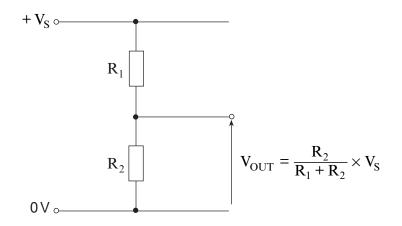

- 6. Voltage Divider

- 7. **Power** = voltage × current;  $P = VI = I^2R = \frac{V^2}{R}$ .

- 8. LED The forward voltage drop across a LED is 2 V.

- 9. NPN Transistors (i) Current gain =  $\frac{\text{Collector current}}{\text{Base current}}$ ;  $h_{FE} = \frac{I_C}{I_B}$ .

- (ii) The forward voltage drop across the base emitter junction is 0.7 V.

# 10. Amplifiers

Voltage gain:  $A = \frac{V_{OUT}}{V_{IN}}$

Non-inverting amplifier:

$$A = 1 + \frac{R_F}{R_1}$$

Inverting amplifier:

$$A = -\frac{R_F}{R_{IN}}$$

Summing amplifier:

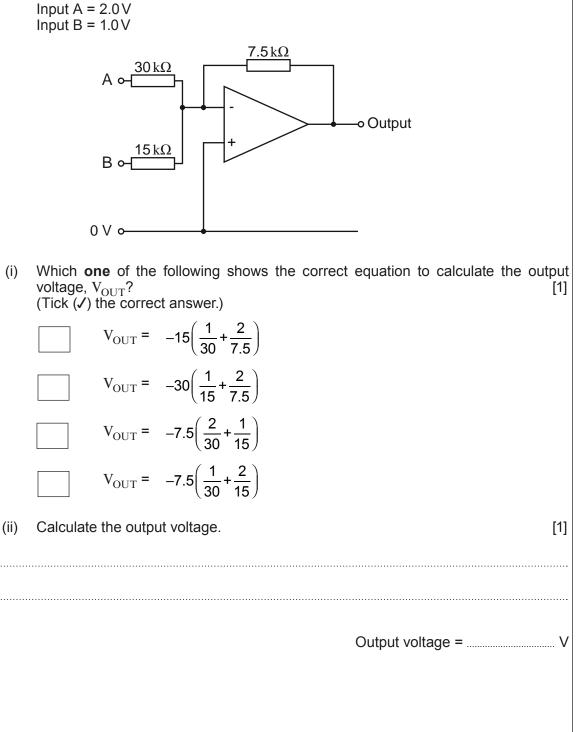

$$V_{OUT} = -R_F \left( \frac{V_1}{R_1} + \frac{V_2}{R_2} + \dots \right)$$

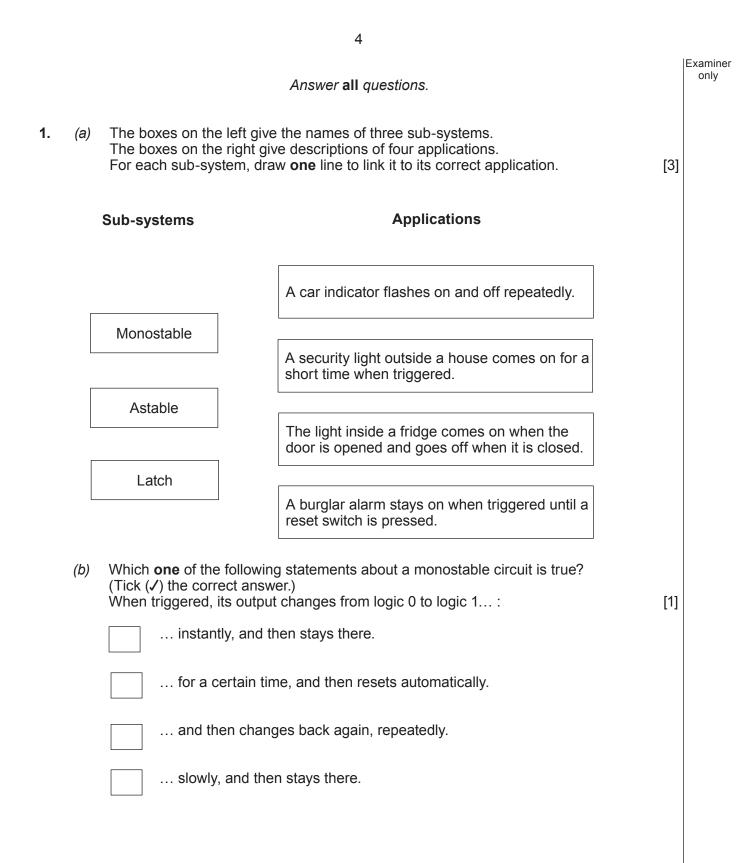

(c) Which one of the following shows the circuit diagram for a monostable circuit based on a 555 timer?

(Tick (✓) the correct answer.) [1]

5

0V c

Turn over.

4162 010005

Examiner only

Output

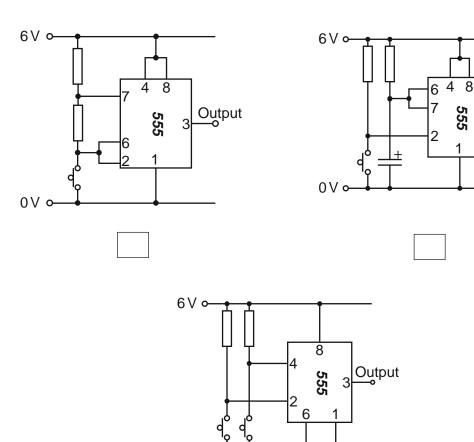

only Here are four signals produced by astable circuits: (a) Voltage / V 12 Α 6 ► Time / s 0 ż 3 0 1 Voltage / V 12 В 6 Time / s 0 Ż 0 3 1 Voltage / V 12 🕇 С 6 0 Time / s 2 0 3 1 Voltage / V 12 D 6 ► Time / s 0 0 2 3 1 (i) Which two signals have the same amplitude? [1] Answer: and Which two signals have the same period? (ii) [1] Answer: and An astable sub-system has a period of ten seconds. (b) Calculate its frequency in Hz. [1] Answer = ..... Hz

6

Examiner

Examiner only

> 4162 010007

[1]

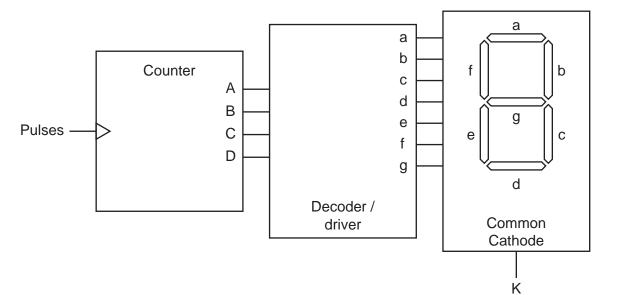

(a) The LED segments of a 7-segment display light when they receive logic 1 signals. The display needs to show the letter 'H'. Complete the truth table by selecting 0 or 1 for each segment to make the display.

7

| Segments |   |   |   |   |   |   | Character |  |

|----------|---|---|---|---|---|---|-----------|--|

| а        | b | С | d | е | f | g | Character |  |

|          |   |   |   |   |   |   | Н         |  |

f g c d

(b) The display is used in the single digit decimal counting system, shown in the diagram.

Which row in the table produces '7' on the display? (Tick (✓) the correct answer.)

| Decoder / driver outputs |   |   |   |   |   |   |  |  |  |  |

|--------------------------|---|---|---|---|---|---|--|--|--|--|

| a b c d e f g            |   |   |   |   |   |   |  |  |  |  |

| 0                        | 0 | 0 | 0 | 1 | 1 | 1 |  |  |  |  |

| 1                        | 1 | 1 | 0 | 0 | 0 | 0 |  |  |  |  |

| 1                        | 1 | 0 | 0 | 0 | 1 | 1 |  |  |  |  |

| 0                        | 0 | 1 | 1 | 1 | 0 | 0 |  |  |  |  |

(ii) What connection must be made to the common cathode pin to make the display work? Circle the correct answer. [1]

Connect pin K to

0V 5V Reset Clock

© WJEC CBAC Ltd.

Turn over.

[1]

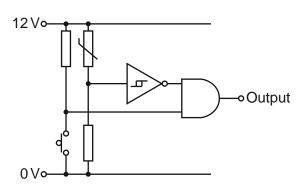

A temperature controller has two input sub-systems – a switch unit and a temperature-sensing unit.

The output of the temperature-sensing unit is interfaced to the logic gate by a Schmitt inverter.

[4]

Write either 'Analogue' or 'Digital' in the box next to the signals listed in the table.

| Signal                             | Analogue or digital? |

|------------------------------------|----------------------|

| Output of temperature-sensing unit |                      |

| Output of switch unit              |                      |

| Output of Schmitt inverter         |                      |

| Output of logic gate               |                      |

Examiner only

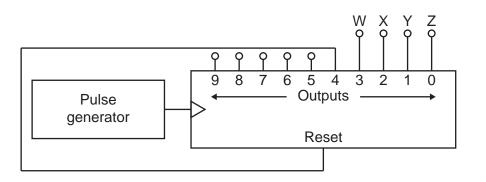

9 Examiner The pinout for a decade counter is shown below. output 5 16 supply + 1 output 1 15 2 reset output 0 3 14 clock 4017B output 2 13 4 enable 5 12 output 6 carry 11 output 7 6 output 9 7 10 output 3 output 4 supply -8 9 output 8 Which statement best describes the function of the decade counter? (a) (Tick ( $\checkmark$ ) the correct answer.) [1] It counts up in tens, not in units. It resets automatically on the sixteenth pulse. Each output goes high in turn. Every tenth count, it outputs a pulse from its clock pin.

5.

only

(b) The diagram shows part of a lighting sequence, controlled by a decade counter. Outputs W, X, Y and Z are connected to LEDs. The counter resets when the Reset pin receives a logic 1 signal.

Complete the table by writing **On** or **Off** for each LED to show the sequence.

| Pulse | LEDs |     |     |     |  |  |  |  |

|-------|------|-----|-----|-----|--|--|--|--|

|       | Z    | Y   | X   | W   |  |  |  |  |

| 0     | On   | Off | Off | Off |  |  |  |  |

| 1     |      |     |     |     |  |  |  |  |

| 2     |      |     |     |     |  |  |  |  |

| 3     |      |     |     |     |  |  |  |  |

| 4     |      |     |     |     |  |  |  |  |

© WJEC CBAC Ltd.

Examiner only

[2]

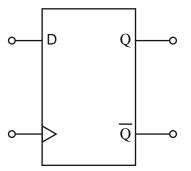

(a) Which of the following statements best describes the behaviour of a D-type flip-flop?

(Tick (✓) the correct answer.) [1]

The  $\overline{Q}$  pin changes state every time a clock pulse triggers the flip-flop.

The clock is triggered when the D pin changes state.

The  $\boldsymbol{Q}$  pin copies the logic level on the D pin when the flip-flop is triggered.

The D pin copies the logic level on the clock pin when the flip-flop is triggered.

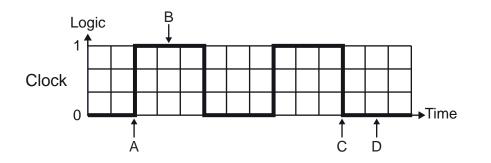

(b) A D-type flip-flop is rising-edge triggered.

6.

On the graph, which arrow identifies a rising-edge of a clock pulse? Circle the correct answer.

A B C D

11

4162 010011

Examiner only

[1]

(4162-01)

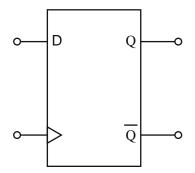

7. A rising-edge triggered D-type flip-flop can be made into a one-bit counter.

(a) Which connection should be made to create a one-bit counter?

(Tick (✓) the correct answer.)

Q output to the D input.

$\overline{\mathrm{Q}}$  output to the D input.

- $\overline{\mathbf{Q}}$  output to the clock input.

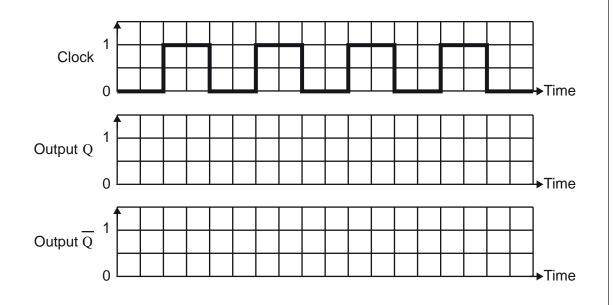

- (b) Initially, the one-bit counter is reset. Use the axes provided to draw the corresponding signals on the Q and  $\overline{Q}$  outputs. [3]

Examiner only

[1]

13

Turn over.

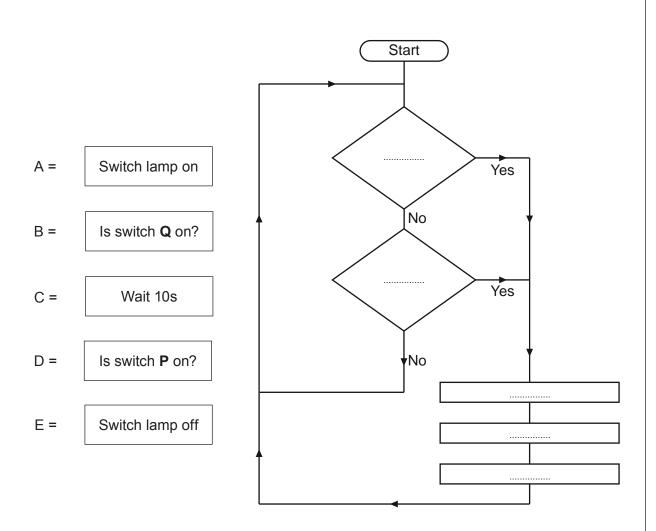

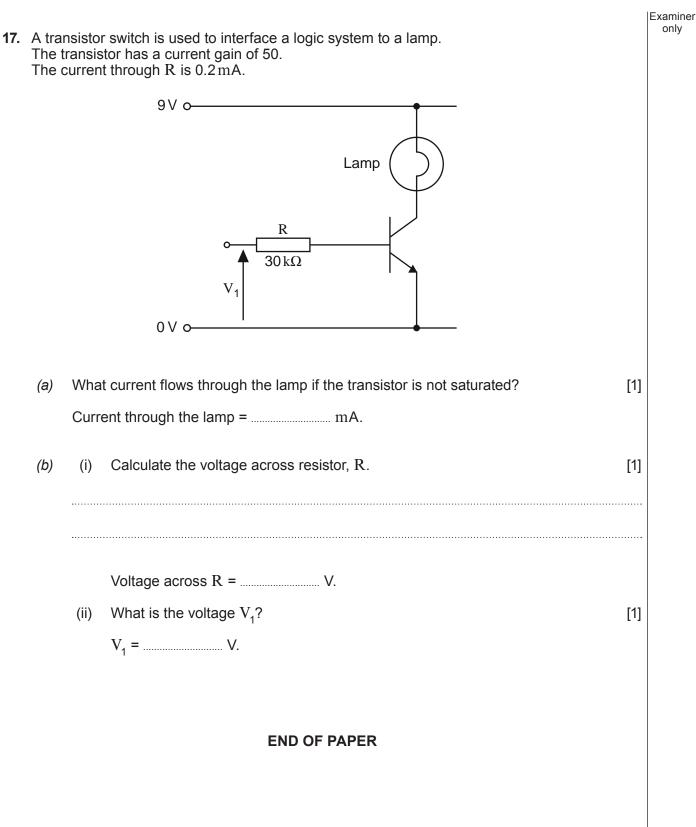

**9.** A microcontroller is used to operate a lamp in a dark corridor, using two push-switches **P** and **Q** located at the ends of the corridor.

Examiner

[4]

When switch **P** OR switch **Q** is pressed for a moment, the light comes on for ten seconds.

Complete the flowchart by writing the correct letter in the boxes.

15

10.

| Comp | parators a                                                                                                           | and Schmitt inverters can be used to interface a light-sensing unit to a logic syster                           | Examiner<br>only<br>1. |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|--|

| (a)  | <ul> <li>(a) Which statement about the comparator is correct? [1]</li> <li>(Tick (✓) the correct answer.)</li> </ul> |                                                                                                                 |                        |  |  |  |  |

|      |                                                                                                                      | It has a single switching threshold fixed at 0.7 V.                                                             |                        |  |  |  |  |

|      |                                                                                                                      | It has a single switching threshold at a voltage which can be varied.                                           |                        |  |  |  |  |

|      |                                                                                                                      | It has two fixed switching thresholds.                                                                          |                        |  |  |  |  |

|      |                                                                                                                      | It has two switching thresholds at voltages which can be varied.                                                |                        |  |  |  |  |

| (b)  | applicat                                                                                                             | statement gives the advantage of a Schmitt inverter over the comparator in th<br>ion?<br>) the correct answer.) | is<br>1]               |  |  |  |  |

|      |                                                                                                                      | It stops contact bounce in the light sensor.                                                                    |                        |  |  |  |  |

|      |                                                                                                                      | It stops rapid output switching when the light level fluctuates slightly.                                       |                        |  |  |  |  |

|      |                                                                                                                      | It works better in the dark.                                                                                    |                        |  |  |  |  |

|      |                                                                                                                      | It boosts the current to the logic system.                                                                      |                        |  |  |  |  |

|      |                                                                                                                      |                                                                                                                 |                        |  |  |  |  |

|      |                                                                                                                      |                                                                                                                 |                        |  |  |  |  |

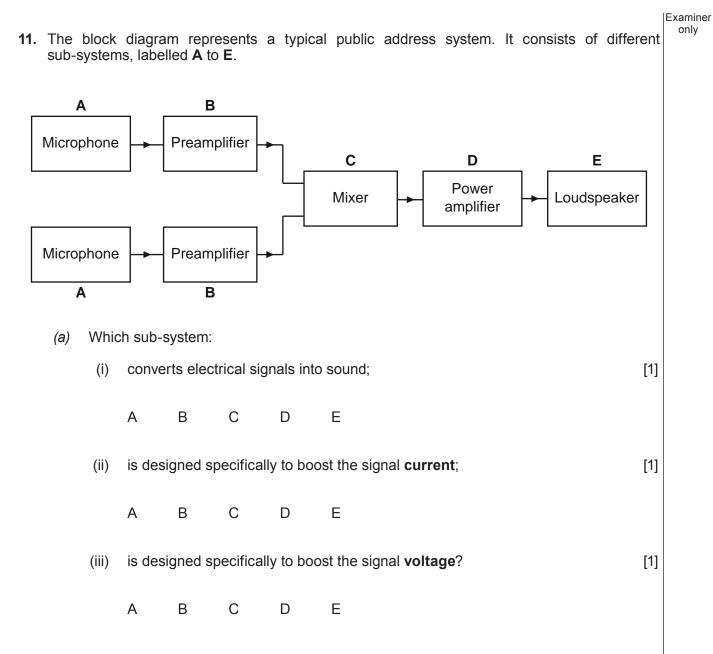

(b) The mixer, shown in the diagram, combines signals from the two microphones. It is tested by applying the following voltages.

(4162-01)

Examiner only

- **12. A**, **B** and **C** are different voltage amplifiers.

- (a) When the input signal has an amplitude of 4 mV, amplifier A produces an output signal with an amplitude of 40 mV.

What is the voltage gain of amplifier A? Circle the correct answer. [1]

10 36 44 160

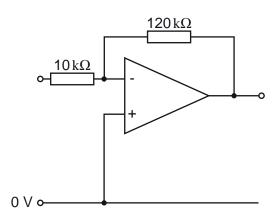

(b) The circuit diagram for amplifier **B** is shown below. What is its voltage gain? Circle the correct answer.

–13 –12 12 13

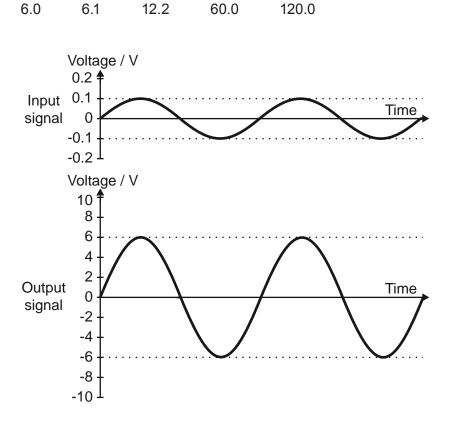

(c) The top graph shows the signal applied to the input of amplifier C.

The bottom graph shows the corresponding output signal.

What is the voltage gain of amplifier C? Circle the correct answer.

Examiner only

[1]

[1]

© WJEC CBAC Ltd.

19 Examiner only **13.** The block diagram for a sequence controller is shown below. Pulse LED Counter Memory generator array Address Data lines lines The contents of the memory are given in the following table: Address Data **A**<sub>1</sub>  $D_1$  $D_3$  $D_2$ D<sub>0</sub>  $A_2$ A<sub>0</sub> 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 1 0 0 1 0 0 1 0 1 0 0 1 0 1 0 0 0 0 0 1 What is the minimum number of bits that the counter must have? (a) Circle the correct answer. [1] 1 2 3 4 5 (b) Each output is connected to a single LED. How many LEDs are required in total? Circle the correct answer. [1] 1 2 3 4 5 (C) Initially, the counter is reset. How many pulses are then needed to produce the output '0100'? Circle the correct answer. [1] 2 3 1 4 5

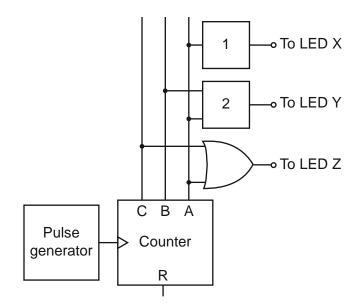

**14.** The diagram shows part of a control system for a LED lighting sequence.

A LED lights when it receives a logic 1 signal.

The behaviour of LEDs X and Y is shown in the table.

| Pulses |   | Counter<br>outputs | LEDs |     |     |

|--------|---|--------------------|------|-----|-----|

|        | С | В                  | Α    | X   | Y   |

| 0      | 0 | 0                  | 0    | On  | On  |

| 1      | 0 | 0                  | 1    | Off | On  |

| 2      | 0 | 1                  | 0    | On  | On  |

| 3      | 0 | 1                  | 1    | Off | Off |

| 4      | 1 | 0                  | 0    | On  | On  |

| 5      | 1 | 0                  | 1    | Off | On  |

| 6      | 1 | 1                  | 0    | On  | On  |

| 7      | 1 | 1                  | 1    | Off | Off |

| (a) | Box 1 mu                     | ıst contain                 | the                              | logic          | gate.          |                                        |    | E   | Examiner<br>only |

|-----|------------------------------|-----------------------------|----------------------------------|----------------|----------------|----------------------------------------|----|-----|------------------|

|     |                              |                             | nswer from t                     |                |                |                                        |    | [1] |                  |

|     | NOT                          | AND                         | NAND                             | OR             | NOR            |                                        |    |     |                  |

| (b) | Box 2 mu<br>Insert the       | ist contain<br>correct ai   | the<br>nswer from t              | the list belo  | c gate.<br>ow. |                                        |    | [1] |                  |

|     | NOT                          | AND                         | NAND                             | OR             | NOR            |                                        |    |     |                  |

| (C) | Which tw                     | o pulses c                  | ause LED Z                       | to switch      | off?           |                                        |    |     |                  |

|     |                              |                             | and<br>nswers from               |                |                | Z to switch off                        |    | [2] |                  |

|     | 0 1                          | 2                           | 3 4                              | 5              | 6              | 7                                      |    |     |                  |

| (d) | The next                     | diagram ir                  | ncludes the                      | reset sub-s    | system.        |                                        |    |     |                  |

|     |                              |                             |                                  |                | 1              | ⊸ To LED X<br>⊸ To LED Y<br>⊸ To LED Z |    |     |                  |

|     |                              | Puls<br>genera              |                                  | B A<br>Counter |                |                                        |    |     |                  |

|     |                              |                             | when the re<br>ox <b>W</b> makes |                |                | a logic 1 signa<br>on pulse 6.         | Ι. |     |                  |

|     | Box <b>W</b> m<br>Insert the | ust contair<br>e correct ar | n the<br>nswer from t            | the list belo  | c gate.<br>ow. |                                        |    | [1] |                  |

|     | NOT                          | AND                         | NAND                             | OR             | NOR            |                                        |    |     |                  |

|     |                              |                             |                                  |                |                |                                        |    |     |                  |

21

(4162-01)

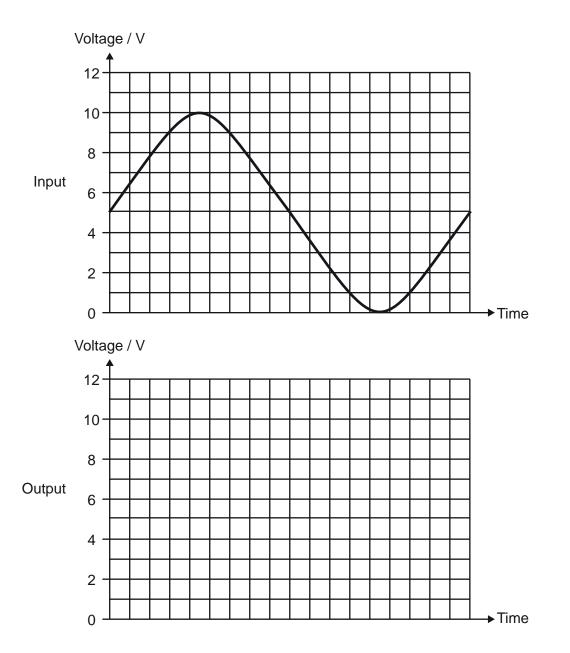

**15.** A Schmitt Inverter is tested using the input signal shown in the upper graph.

### **Schmitt Inverter Information:**

The output:

- changes from logic 1 to logic 0 when a **rising** input voltage reaches 9V;

- changes from logic 0 to logic 1 when a falling input voltage reaches 6 V.

A signal at 1V represents logic 0 and one at 10V represents logic 1.

Use the axes provided in the lower graph to draw the expected output signal.

Examiner only

[4]

# **BLANK PAGE**

23

Turn over.

#### Examiner only **16.** A **non-inverting** amplifier has a voltage gain of 12. The graph shows the input signal of peak value 0.25 V. (a) Draw the wave that shows the corresponding output signal in the graph below. [2] Voltage / V 4.0 3.0 2.0 1.0 0.25 -0 ----- - -→ Time / ms 0.8 0.1 0.2 0.3 0.4-0.5-0.6 0.7 -1.0 -2.0 -3.0 -4.0

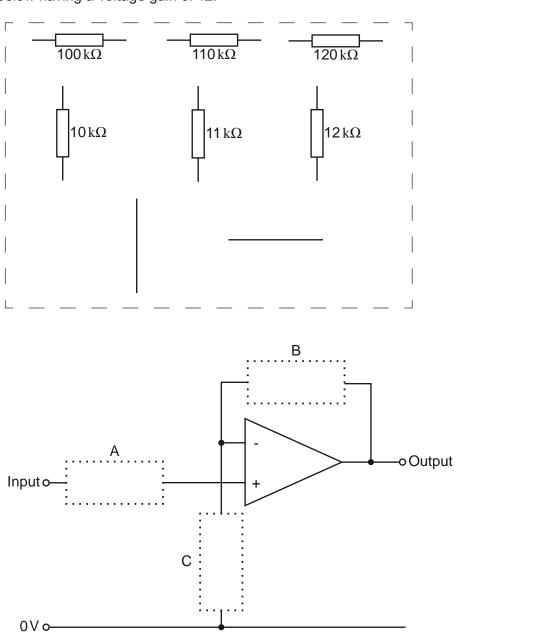

(b) Draw the correct components in the circuit diagram for the non-inverting amplifier shown below having a voltage gain of 12.

Turn over.

Examiner

# **BLANK PAGE**